Published

Channel Operating Margin Exploration as a Complementary Transceiver Circuit Design Tool for 25 Gbps PAM4 Serial Links

Exploración del margen operativo del canal como herramienta complementaria para el diseño de circuitos transceptores con enlaces seriales PAM4 de 25 Gbps

Keywords:

COM, Equalizers, IEEE 802.3ck, eye diagram, single-bit response (en)COM, ecualizadores, IEEE 802.3ck, diagrama de ojo, respuesta a único bit (es)

Downloads

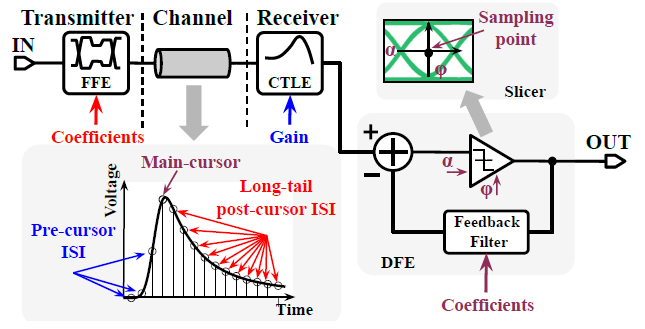

The design of high-speed serial links continues to attract the attention of the electronics industry due to the steady development of different telecommunications standards, generating a constantly growing data rate and new modulation schemes. However, conventional certification metrics can lead to sub-optimal transmit (Tx) and receive (Rx) circuit designs. Therefore, the Ethernet standard IEEE 802.3bj introduced a more effective evaluation method called channel operating margin (COM) to explore the design space at an early stage. Although the advantages of COM have been discussed in the literature and only a few works explore its potential as a backplane design tool, there are no reports on the use of COM as a complementary design tool for transceiver circuits. This work studies the use of COM as a complementary tool for transceiver design. COM performance is evaluated for four 100GBASE-KP4 backplanes and different equalization architectures. The impact of the metric and the challenges associated with incorporating new equalization structures into the COM flow are discussed. The results reveal a conventional Tx-Rx architecture that exceeds the COM threshold and an alternative one that improves the opening of the eye diagram but does not exceed the threshold.

El diseño de enlaces seriales de alta velocidad continúa atrayendo la atención de la industria electrónica debido al desarrollo constante de diferentes estándares de telecomunicaciones, generando una tasa de datos en constante crecimiento y nuevos esquemas de modulación. Sin embargo, las métricas de certificación convencionales pueden llevar a diseños de circuitos de transmisión (Tx) y recepción (Rx) subóptimos. Por lo tanto, el estándar Ethernet IEEE 802.3bj introdujo un método de evaluación más efectivo llamado margen de operación del canal (COM, por sus siglas en inglés) para explorar el espacio de diseño en una etapa temprana. Aunque las ventajas de COM han sido discutidas en la literatura y solo unos pocos trabajos exploran su potencial como una herramienta de diseño de backplane, no hay informes sobre el uso de COM como una herramienta de diseño complementaria para circuitos transceptores. Este trabajo estudia el uso de COM como una herramienta complementaria para el diseño de transceptores. El rendimiento de COM se evalúa para cuatro backplanes 100GBASE-KP4 y diferentes arquitecturas de ecualización. Se discuten el impacto de la métrica y los desafíos asociados a la incorporación de nuevas estructuras de ecualización en el flujo de COM. Los resultados revelan una arquitectura Tx-Rx convencional que supera el umbral de COM y una alternativa que mejora la apertura del diagrama de ojo pero no supera el umbral de COM.

Downloads

References

Anritsu Company. (2016). White Paper: Measuring Channel Operating Margin. https://dl.cdn-anritsu.com/en-us/test-measurement/files/Technical-Notes/White-Paper/11410-00989A.pdf

Champion, B., & Tracy, N. (2019). Delivering 100 gbps solutions for chip-to-module and direct attach copper (dac) cable implementations. https://www.te.com/content/dam/te-com/documents/datacomm/global/delivering-100-gbps-solutions-for-chip-paper.pdf

Chen, K.-Y., Chen, W.-Y., & Liu, S.-I. (2017). A 0.31-pJ/bit 20Gb/s DFE with 1 discrete tap and 2 IIR filters feedback in 40-nm-LP CMOS. IEEE Transactions on Circuits and Systems II: Express Briefs, 64(11), 1282-1286. https://doi.org/10.1109/TCSII.2016.2645698

de Paulis, F., Rabinovich, R., Mellitz, R., & Resso, M. (2022). Feasibility analysis of chip-to-module channel operating at 212 Gbps. In IEEE (Eds.), 2022 IEEE 26th Workshop on Signal and Power Integrity (SPI) (pp. 1-4). IEEE. https://doi.org/10.1109/SPI54345.2022.9874926

de Paulis, F., Wang-Lee, T., Mellitz, R., Resso, M., Rabinovich, R., & Danzy, O. (2020). Backplane channel design exploration at 112 Gbps using channel operating margin (COM). In IEEE (Eds.), 2020 IEEE International Symposium on Electromagnetic Compatibility Signal/Power Integrity (EMCSI) (pp. 158-163). IEEE. https://doi.org/10.1109/EMCSI38923.2020.9191569

Dong, X., Mo, M., Rao, W., Jin, F., & G, Z. (2014). Relating COM to familiar S-parameter parametric to assist 25Gbps system design. DesignCon 2014. https://www.xilinx.com/content/dam/xilinx/publications/events/designcon/2014/8_TU2Slides_RelatingCOMtoFamiliarS_ParameterParametrictoAssist25GbpsSystemDesign.pdf

Dovale, L., & Roa, E. (2021). Channel operating margin as transceiver architecture design tool. In IEEE (Eds.), 2021 IEEE International Symposium on Circuits and Systems (ISCAS) (pp. 1-5). IEEE. https://doi.org/10.1109/ISCAS51556.2021.9401322

Elhadidy, O., & Palermo, S. (2013). A 10 Gb/s 2-IIR-tap DFE receiver with 35 dB loss compensation in 65-nm CMOS. In 2013 Symposium on VLSI Circuits (pp. C272-C273).

Filip, C. (2018). Effective return loss, a new metric for SerDes channel or package characterization. Mentor, A Siemens Business.

Gore, B., & Mellitz, R. (2014). An exercise in applying channel operating margin (COM) for 10GBASE-KR channel design. In IEEE (Eds.), 2014 IEEE International Symposium On Electromagnetic Compatibility (EMC) (pp. 648-653). IEEE. https://doi.org/10.1109/ISEMC.2014.6899050

Heck, H., & Intel. (2018). Server backplane channels. IEEE P802.3ck Task Force - Tools and Channels, November 2018. Retrieved from http://www.ieee802.org/3/100GEL/public/tools

IEEE. (2014). IEEE Standard for Ethernet Amendment 2: Physical Layer Specifications and Management Parameters for 100 Gb/s Operation Over Backplanes and Copper Cables. IEEE Std 802.3bj-2014 (Amendment to IEEE Std 802.3-2012 as amended by IEEE Std 802.3bk-2013), 1-368.

IEEE. (2018). IEEE 802.3ck 100 [Gb/s] per Electrical Lane Objectives. IEEE Std 802.3-2018 (Adopted by Study Group). Retrieved from https://www.ieee802.org/3/100GEL/P802_3ck_Objectives_2018mar.pdf

Kim, B., Liu, Y., Dickson, T. O., Bulzacchelli, J. F., & Friedman, D. J. (2009). A 10-Gb/s compact low-power serial I/O with DFE-IIR equalization in 65-nm CMOS. IEEE Journal of Solid-State Circuits, 44(12), 3526-3538. https://doi.org/10.1109/JSSC.2009.2031015

Lee, J., Chiang, P.-C., Peng, P.-J., Chen, L.-Y., & Weng, C.-C. (2015). Design of 56 Gb/s NRZ and PAM4 SerDes transceivers in CMOS technologies. IEEE Journal of Solid State Circuits, 50(9), 2061-2073. https://doi.org/10.1109/JSSC.2015.2433269

Mellitz, R., Abbott, J., & Samtec. (2018). 112G cabled backplane channel and PCB design impact using 112G ready connectors. IEEE P802.3ck Task Force - Tools and Channels. https://www.ieee802.org/3/ck/public/adhoc/aug15_18/mellitz_3ck_adhoc_02_081518.pdf

Mueller, K., & Muller, M. (1976). Timing recovery in digital synchronous data receivers. IEEE Transactions on Communications, 24(5), 516-531. https://doi.org/10.1109/TCOM.1976.1093326

Palkert, T., & Molex. (2020). OD backplane channel analysis. IEEE P802.3ck Task Force - Tools and Channels, January 2020. Retrieved from http://www.ieee802.org/3/100GEL/public/tools

Peng, P.-J., Lee, P.-L., Huang, H.-E., Huang, W.-J., Lin, M.-W., Juang, Y.-Z., & Tseng, S.-H. (2022). A 56-Gb/s PAM-4 transmitter/receiver chipset with nonlinear FFE for VCSEL-based optical links in 40-nm CMOS. IEEE Journal of Solid-State Circuits, 57(10), 3025-3035. https://doi.org/10.1109/JSSC.2022.3192711

Roshan-Zamir, A., Elhadidy, O., Yang, H.-W., & Palermo, S. (2017). A reconfigurable 16/32 Gb/s dual-mode NRZ/PAM4 SerDes in 65-nm CMOS. IEEE Journal of Solid-State Circuits, 52(9), 2430-2447. https://doi.org/10.1109/JSSC.2017.2705070

Shahramian, S., & Chan Carusone, A. (2015). A 0.41 pJ/bit 10 Gb/s hybrid 2 IIR and 1 discrete-time DFE tap in 28 nm-LP CMOS. IEEE Journal of Solid-State Circuits, 50(7), 1722-1735. https://doi.org/10.1109/JSSC.2015.2402218

Shahramian, S., Dehlaghi, B., & Chan Carusone, A. (2016). Edge-based adaptation for a 1 IIR + 1 discrete-time tap DFE converging in 5 μs. IEEE Journal of Solid-State Circuits, 51(12), 3192-3203. https://doi.org/10.1109/JSSC.2016.2594209

License

Copyright (c) 2024 Luisa Fernanda Dovale-Vargas, Oscar Mauricio Reyes-Torres, Elkim Felipe Roa-Fuentes

This work is licensed under a Creative Commons Attribution 4.0 International License.

The authors or holders of the copyright for each article hereby confer exclusive, limited and free authorization on the Universidad Nacional de Colombia's journal Ingeniería e Investigación concerning the aforementioned article which, once it has been evaluated and approved, will be submitted for publication, in line with the following items:

1. The version which has been corrected according to the evaluators' suggestions will be remitted and it will be made clear whether the aforementioned article is an unedited document regarding which the rights to be authorized are held and total responsibility will be assumed by the authors for the content of the work being submitted to Ingeniería e Investigación, the Universidad Nacional de Colombia and third-parties;

2. The authorization conferred on the journal will come into force from the date on which it is included in the respective volume and issue of Ingeniería e Investigación in the Open Journal Systems and on the journal's main page (https://revistas.unal.edu.co/index.php/ingeinv), as well as in different databases and indices in which the publication is indexed;

3. The authors authorize the Universidad Nacional de Colombia's journal Ingeniería e Investigación to publish the document in whatever required format (printed, digital, electronic or whatsoever known or yet to be discovered form) and authorize Ingeniería e Investigación to include the work in any indices and/or search engines deemed necessary for promoting its diffusion;

4. The authors accept that such authorization is given free of charge and they, therefore, waive any right to receive remuneration from the publication, distribution, public communication and any use whatsoever referred to in the terms of this authorization.